由于所有芯片都出现在PCI或PCIe卡上,因此布局和布线这些电路板似乎非常复杂。但是,PCIe的标准化体系结构为设计人员提供了相当大的灵活性。

一个有点复杂的问题是这些卡上组件的PCIe BGA扇出。实施扇出和逃逸路由策略的技巧是确保您符合PCIe布局和路由规范。考虑到这一点,让我们深入研究扇出和转义路由的一些技巧。

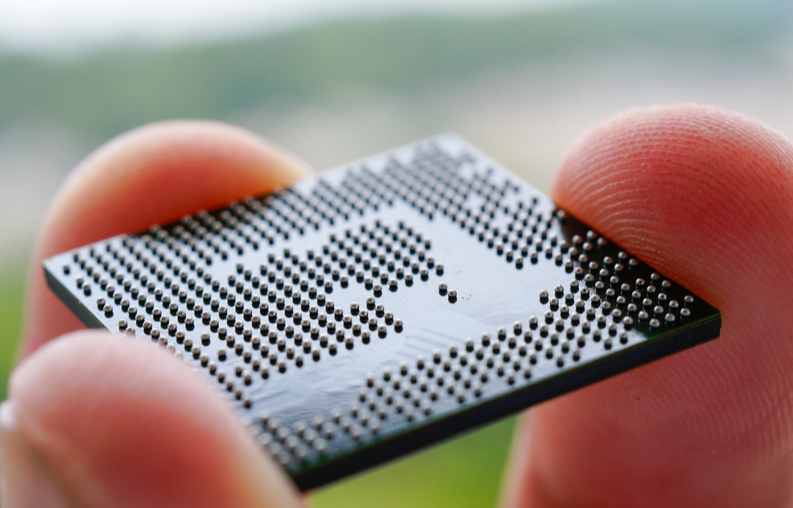

PCIe BGA扇出

与大多数带有BGA的组件一样,没有关于BGA扇出的黄金法则,正确的选择取决于BGA中球之间的间距。组件制造商可能会针对特定组件推荐不同的扇出策略,因此,最好在实施扇出策略之前检查其数据表。

实际的逃生路由策略将部分取决于层堆栈。PCIe设备主要构建在4层电路板上,尽管6层线路板也是常见的选择。无论层数如何,卡的总厚度都限制为1.57 mm。对于四层线路板,由于有两个内部铜层,因此布线空间将限制为两层。

使用间距非常粗的BGA,您可能可以直接将其引出封装,而无需在信号线上放置过孔。PCIe路由准则甚至在BGA下也指定了对称路由。当您在相邻球之间的包装下方布线时,可能需要在信号线上放置一个弯头以进行所需的连接。尝试尽可能接近地镜像差分对上两条走线的任何弯曲。最好在焊盘之间布线差分对,而不要在一对走线之间放置焊盘。

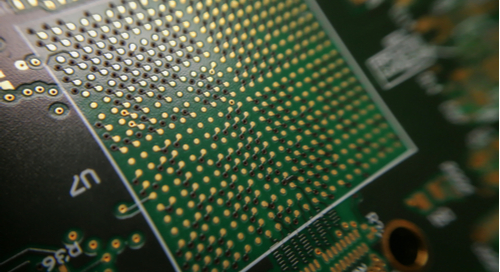

狗骨头扇出策略适合于粗间距到中等间距的BGA,但诀窍是使走线保持在封装下方。考虑到板厚度的限制,这可能很困难,因为这限制了可用的层数。实际上,与典型的狗骨头扇出策略相比,在球之间路由差分对的要求实际上使得更容易直接在顶部信号层(即,无过孔)上到达BGA中的前两行。然后,在内部的行上,可以使用带有通孔的狗骨头扇出结构到达另一个信号层。穿过铜层布线时,请确保包括合适的防垫直径。

对于极高间距的BGA,其引脚数非常高,您可能别无选择,只能通过HDI路由选择更高的层数。由于所需连接的剪切数,精细的BGA间距可能不支持典型的扇出策略。您将要使用VIPPO通孔来访问电路板的内层,因为VIPPO中的镀层可以防止焊料芯吸到电路板的背面。

BGA的典型狗骨头扇出

转义后路由

一旦您的迹线从BGA中逸出,接下来会发生什么情况取决于要安装在BGA上的设备。尽管正式的PCIe布局和路由规范定义了允许的最大走线长度,差分阻抗值和互连上可能出现的最大通孔数量,但您的组件可能会具有不同的要求。BGA外部的路由规范更多地取决于所使用的组件和信令标准,而不仅仅是查看PCIe标准中的最大允许量。

由于组件本身的敏感公差,使用不同组件产生的这些变化的最小,典型和最大布线要求。这些要求往往比正式PCIe标准中提供的限额更为严格,无论其年代如何。因此,在开始设计布局和布线之前,应始终检查组件的数据表。

要使阻抗差分迹线保持一致并在所需的公差范围内,可以采用具有受控阻抗设计和布线功能的PCB设计软件。这允许自动路由或交互式路由功能在您路由时自动设置迹线间距和几何形状。确保遵守差分对之间的间距的“ 5W”规则,并镜像相邻走线中一条走线的任何偏差,以确保对称性。另外,请确保根据所选的信号传输标准定义长度不匹配的公差。

当今的设备速度要求设计人员定义具有一致特征阻抗的差分走线几何形状,作为符合PCIe标准的设计规则。与规则驱动的PCB设计软件一起使用可极大地简化布局和布线,从而使根据PCIe规范设计电路板变得更加容易。

下一页:如何检查PCB上的短路